Tassonomia di Flynn per i calcolatori elettronici

Gli obbiettivi delle nuove dell’architettura di calcolatori elettronici sono essenzialmente due, alternativi tra loro:

- riduzione del rapporto costo/prestazioni;

- raggiungimento di un’alta scalabilità (la scalabilità è sostanzialmente la possibilità di ripartire lo svolgimento di un dato compito tra più unità funzionali, al fine di sveltire lo svolgimento stesso) affiancata da un soddisfacente rapporto costo/prestazioni.

Essendo che le CPU con parallelismo a livello di istruzioni sfruttano il parallelismo intrinseco di un programma, ossia quello esistente tra le singole istruzioni. Si può però facilmente verificare che il parallelismo di tale tipo è relativamente limitato, salvo applicazioni molto particolari: risulta infatti difficile raggiungere una buona efficienza di uso al di sopra di 8/16 unità funzionali parallele all’interno della singola CPU. A questo, si aggiunge il fatto che esistono applicazioni nelle quali è molto difficile, se non impossibile, individuare parallelismo a livello di istruzione: i sistemi operativi sono un classico esempio a questo proposito.

L’alternativa emersa da alcuni decenni è quella dei cosiddetti sistemi paralleli, nei quali cioè il parallelismo sfruttato è quello a livello di sequenza di istruzioni o di processo: l’architettura, in questi sistemi, è costituita da un certo numero di unità di elaborazione, dotate ognuna di proprie risorse e che interagiscono l’una con l’altra in modo opportuno. Il concetto alla base dei sistemi paralleli è quello per cui, eseguendo simultaneamente più passi di uno stesso problema, si può completare il lavoro molto più velocemente.

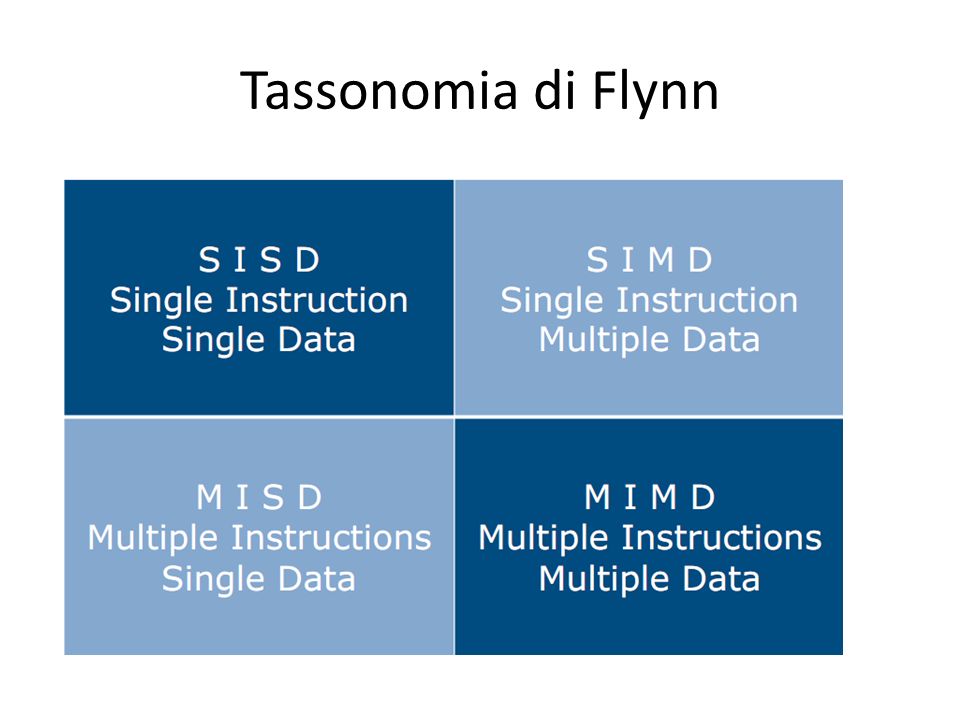

Tassonomia di Flynn

Diversi anni fa, Flynn propose un semplice metodo di classificazione (Tassonomia di Flynn) dei calcolatori, basato sul parallelismo del flusso di istruzioni e del flusso di dati ad esso connesso:

- con flusso di istruzioni intendiamo la sequenza di istruzione eseguite da una unità di elaborazione (un processore);

- con flusso di dati intendiamo invece la sequenza di operandi manipolato dalla suddetta unità di elaborazione.

Flynn propose dunque le seguenti 4 categorie, chiamata classificazione o tassonomia di Flynn:

- macchine SISD (Single Instruction Single Data): flusso di istruzioni unico e flusso di dati unico; sono le classiche macchine monoprocessore di tipo sequenziale;

- macchine SIMD (Single Instruction Multiple Data): esiste un unico flusso di istruzioni, che però viene applicato a più flussi di dati; risono dunque più processori che eseguono simultaneamente la stessa istruzione su dati diversi;

- macchine MISD (Multiple Instruction Singole Data): esiste un unico flusso di dati, cui però vengono applicati diversi flussi di istruzioni; in pratica, più processori eseguono in maniera autonoma istruzioni diverse sullo stesso flusso di dati;

- macchine MIMD (Multiple Instruction Multiple Data): in quest’ultimo caso, più processori eseguono in maniera autonomia istruzioni diverse su dati diversi.

Limiti della tassonomia di Flynn e nuova classificazione

La tassonomia di Flynn (che suddivide le architetture dei calcolatori in SISD, SIMD, MISD e MIMD), per quanto molto semplice, appare oggi insufficiente per classificare i calcolatori presenti sul mercato. Ad esempio, i cosiddetti processori vettoriali in pipeline possono essere considerati come macchine parallele, ma difficilmente li si può classificare secondo Flynn: infatti, non sono macchine di tipo SIMD in quanto non hanno più processori che eseguono la stessa istruzione, né possono essere viste come macchine MIMD in quanto non sono asincrone.

Una classificazione senz’altro più attuabile, al giorno d’oggi, è quella che individua le seguenti categorie:

- architetture sincrone:

- processori vettoriali in pipeline;

- processori SIMD del tipo processor array;

- processori SIMD del tipo associative memory;

- processori sistolici;

- architetture MIMD:

- architetture a memoria distribuita;

- architetture a memoria condivisa;

- paradigmi MIMD:

- calcolatori ibridi MIMD/SIMD;

- calcolatori data flow;

- calcolatori di riduzione;

- calcolatori wave front.